# Fully Integrated Half-Bridge Module

#### **FEATURES**

- 24 A continuous output current

- •32 A for A-grade

- 1MHz switching frequency

- 650 V supply voltage

- Integrated gate drive with under-voltage lock-out and active Miller clamping

- Compact surface mount package (23.3 mm x 23.3 mm) with top-side heat sinking

### **APPLICATIONS**

- DC/AC or DC/DC converters

- Motor Drive

### **DESCRIPTION**

The SA111 • SA111A is a fully integrated half bridge module based on Silicon Carbide technology. The half bridge provides up to 32 A continuous output current with microcontroller or DSP control. Protection features include under-voltage lockout (UVLO) function and active Miller clamping.

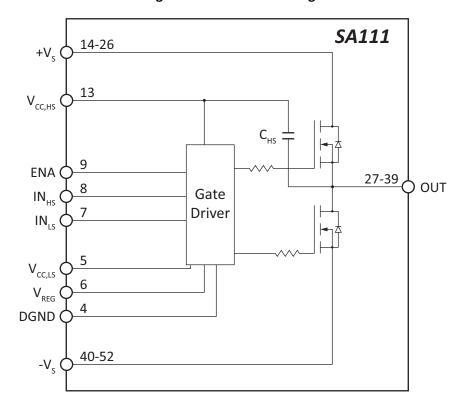

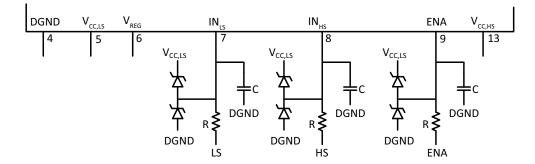

Figure 1: Module Block Diagram

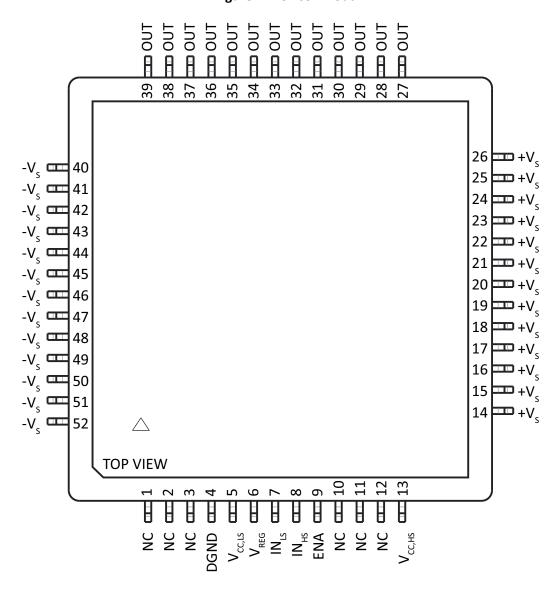

**Figure 2: Device Pinout**

### **PIN DESCRIPTION TABLE**

| Pin Number | Name                | Description                                                                                                           |

|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1-3        | NC                  | Not connected.                                                                                                        |

| 4          | DGND                | Input side ground pin. This pin needs to be connected externally to the negative supply rail or the power ground      |

| 5          | +V <sub>CC,LS</sub> | Low-side and input side power supply pin                                                                              |

| 6          | V <sub>REG</sub>    | Internal power supply output pin. Pin must be connect to DGND with a $1~\mu F$ bypass capacitor.                      |

| 7          | IN <sub>LS</sub>    | Logic input for low-side SiC MOSFET control                                                                           |

| 8          | IN <sub>HS</sub>    | Logic input for high-side SiC MOSFET control                                                                          |

| 9          | ENA                 | Enable pin. A low level puts the high-side and low-side MOSFETs in high-impedance state. See logic table for details. |

| 10-12      | NC                  | Not connected.                                                                                                        |

| 13         | +V <sub>CC,HS</sub> | High-side gate drive power supply                                                                                     |

| 14-26      | +V <sub>S</sub>     | Positive supply rail                                                                                                  |

| 27-39      | OUT                 | PWM output                                                                                                            |

| 40-52      | -V <sub>S</sub>     | Negative supply rail or power ground.                                                                                 |

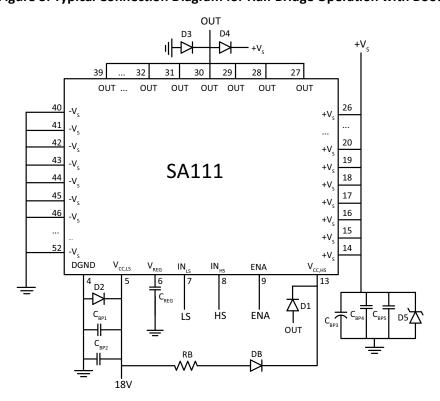

Figure 3: Typical Connection Diagram for Half Bridge Operation with Bootstrap

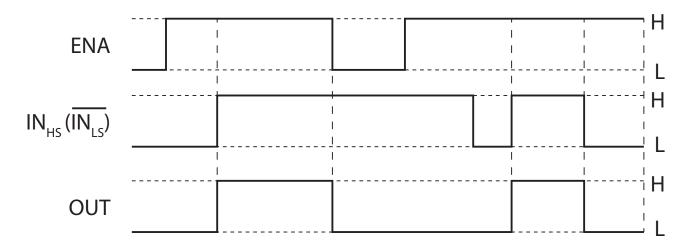

# I/O CONDITION TABLE

| ENA | IN <sub>HS</sub> | IN <sub>LS</sub> | OUT             |

|-----|------------------|------------------|-----------------|

| L   | Х                | Х                | High impedance  |

| Н   | L                | L                | High impedance  |

| Н   | Н                | L                | +V <sub>S</sub> |

| Н   | L                | Н                | -V <sub>S</sub> |

| Н   | Н                | Н                | High impedance  |

Figure 4: Input and Output Logic Timing Chart

# **DEVICE SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                           | Symbol                             | Min  | Max                 | Unit |

|-----------------------------------------------------|------------------------------------|------|---------------------|------|

| Supply Voltage, total                               | +V <sub>S</sub> to -V <sub>S</sub> |      | 650                 | V    |

| Gate Driver Supply Voltage                          | +V <sub>CC</sub>                   |      | 22(rel.)            | V    |

| Output Current, continuous, SA111 • SA111A          |                                    |      | 24                  | А    |

| Output Current, continuous, SA111 • SA111AA         |                                    |      | 32                  | Α    |

| Power Dissipation, internal, continuous, per MOSFET | $P_{D}$                            |      | 56                  | W    |

| Switching Frequency <sup>1</sup>                    |                                    |      | 1000                | kHz  |

| Input Voltage, logic level                          |                                    | -0.3 | +V <sub>CC,LS</sub> | V    |

| Temperature, pin solder, 10s max.                   |                                    |      | 260                 | °C   |

| Temperature, junction, MOSFET                       | T <sub>J</sub>                     |      | 175                 | °C   |

| Temperature Range, storage                          |                                    | -55  | +125                | °C   |

| Operating Temperature Range, case                   | T <sub>C</sub>                     | -40  | +125                | °C   |

<sup>1.</sup> Within SOA. A high frequencies, the switching losses for hard switching might exceed the overall power dissipation of the device. Thus, soft switching is recommended for switching frequencies beyond 200 kHz

## **POWER SUPPLY (SINGLE RAIL SUPPLY)**

| Parameter                                                  | Test Conditions | Min    | Тур    | Max    | Units |

|------------------------------------------------------------|-----------------|--------|--------|--------|-------|

| Low Side Supply Voltage, +V <sub>CC,LS</sub> <sup>1</sup>  |                 | 12     | 18     | 20     | V     |

| Supply Voltage, +V <sub>S</sub>                            |                 |        |        | 650    | V     |

| High Side Supply Voltage, +V <sub>CC,HS</sub> <sup>2</sup> |                 | OUT+12 | OUT+18 | OUT+20 | V     |

| DGND                                                       |                 |        | 0      |        | V     |

- 1. The maximum current might be limited at low temperatures around -25°C when operating the device at V<sub>CC</sub><14V.

- 2. The high-side supply should be realized either as a floating voltage supply relative to the device output or as a bootstrap circuit (resistor and diode in series between +V<sub>CC,LS</sub> and +V<sub>CC,HS</sub>).

### **POWER SUPPLY (DUAL RAIL SUPPLY)**

| Parameter                                                  | Test Conditions | Min                 | Тур                 | Max                 | Units |

|------------------------------------------------------------|-----------------|---------------------|---------------------|---------------------|-------|

| Low Side Supply Voltage, +V <sub>CC,LS</sub> <sup>1</sup>  |                 | -V <sub>S</sub> +12 | -V <sub>S</sub> +18 | -V <sub>S</sub> +20 | V     |

| Total Supply Voltage, +V <sub>S</sub> -(-V <sub>S</sub> )  |                 |                     |                     | 650                 | V     |

| High Side Supply Voltage, +V <sub>CC,HS</sub> <sup>2</sup> |                 | OUT+12              | OUT+18              | OUT+20              | V     |

| DGND                                                       |                 |                     | -V <sub>S</sub>     |                     | V     |

- 1. The maximum current might be limited at low temperatures around -25°C when operating the device at  $V_{CC}$ <14V.

- 2. The high-side supply needs to be a floating supply relative to the device output (or a bootstrap circuit if suitable). The low-side supply voltage is relative to the negative supply rail.

### **INPUT**

| Parameter                                    | Test Conditions                     | Min      | Тур | Max                 | Units |

|----------------------------------------------|-------------------------------------|----------|-----|---------------------|-------|

| Logic High Level Input Voltage               |                                     | DGND+2.0 |     | +V <sub>CC,LS</sub> | V     |

| Logic Low Level Input Voltage                |                                     | DGND     |     | 0.8                 | ٧     |

| Logic Input Minimum Pulse Width <sup>1</sup> | IN <sub>HS</sub> , IN <sub>LS</sub> | 60       |     |                     | ns    |

| ENA Input Mask Time <sup>1</sup>             | ENA                                 | 0.6      | 1.0 | 1.4                 | μs    |

| Isolation                                    |                                     |          | 650 | DGND + 0.8          | ٧     |

1. Guaranteed by design.

### **OUTPUT**

|                                                          |                                                                        | SA1 | 11 • SA1 | L11A | SA111 • SA111AA |     |     |       |

|----------------------------------------------------------|------------------------------------------------------------------------|-----|----------|------|-----------------|-----|-----|-------|

| Parameter                                                | Test<br>Conditions                                                     | Min | Тур      | Max  | Min             | Тур | Max | Units |

| RDS(ON), per MOSFET <sup>1</sup>                         | I <sub>D</sub> =27A,<br>V <sub>CC</sub> =18V,<br>T <sub>J</sub> =25°C  |     | 30       |      |                 | *   |     | mΩ    |

| RDS(ON), per MOSFET <sup>1</sup>                         | I <sub>D</sub> =27A,<br>V <sub>CC</sub> =18V,<br>T <sub>J</sub> =125°C |     | 39.6     |      |                 | *   |     | mΩ    |

| RDS(ON), (Including parasitics)                          | I <sub>D</sub> =27A,<br>V <sub>CC</sub> =18V,<br>T <sub>J</sub> =25°C  |     | 36       |      |                 | *   |     | mΩ    |

| Rise Time, per MOSFET                                    |                                                                        |     | 45       |      |                 | *   |     | ns    |

| Fall Time, per MOSFET                                    |                                                                        |     | 30       |      |                 | *   |     | ns    |

| Switching Frequency <sup>2 3</sup>                       |                                                                        |     |          | 1000 |                 |     | *   | kHz   |

| Current, continuous, source/sink                         |                                                                        | 24  |          |      | 32              |     |     | Α     |

| Current, peak, source/sink <sup>3 4</sup>                |                                                                        |     |          | 50   |                 |     | 80  | Α     |

| Current, continuous, body diode, per MOSFET <sup>3</sup> |                                                                        | 24  |          |      | 32              |     |     | Α     |

| Current, peak, body diode, per<br>MOSFET <sup>3 4</sup>  |                                                                        |     |          | 50   |                 |     | 80  | А     |

| Reverse Recovery Time, body diode, per MOSFET            | $V_S$ =300V,<br>$I_F$ =27A,<br>di/dt=1100A/ $\mu$ s                    |     | 26       |      |                 | *   |     | ns    |

- 1. MOSFET only. Does not consider resistance due to layout/routing.

- 2. Carefully calculate the power dissipation of the device due to conduction and switching losses when operating SA111 SA111A at higher switching frequencies and high output currents. It is recommended to use high switching frequencies only for soft switching (zero current switching) applications

- 3. Guaranteed by design.

- 4. Pulsed.

## THERMAL SPECS

|                              |                    | SA111 • SA111A |     |     |       |

|------------------------------|--------------------|----------------|-----|-----|-------|

| Parameter                    | Test Conditions    | Min            | Тур | Max | Units |

| Resistance, Junction to case | F < 60Hz           |                |     | 2.7 | °C/W  |

| Resistance, Junction to case | F <u>&gt;</u> 60Hz |                |     |     | °C/W  |

| Resistance, Junction to air  |                    |                |     |     | °C/W  |

| Temperature Range, Case      |                    | -40            |     | 125 | °C    |

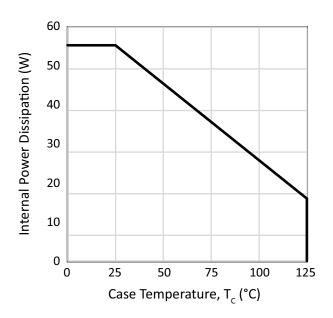

Figure 5: Power Derating

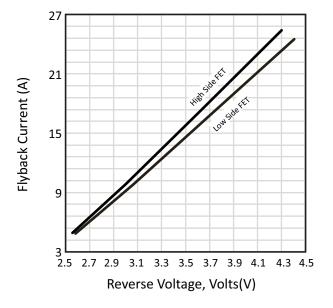

Figure 7: Flyback Current vs. Reverse Voltage

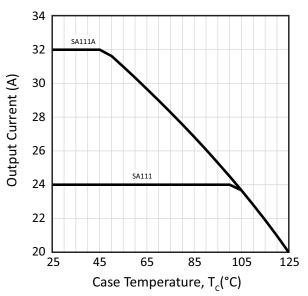

Figure 6: Output Current vs. Temperature

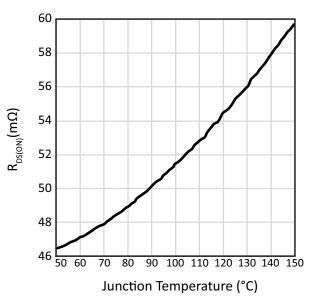

Figure 8:  $R_{DS(ON)}$  vs. Temperature

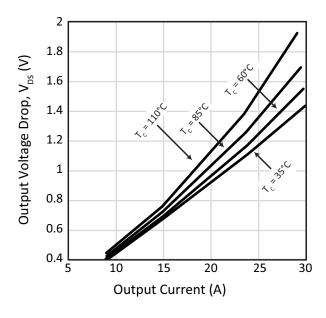

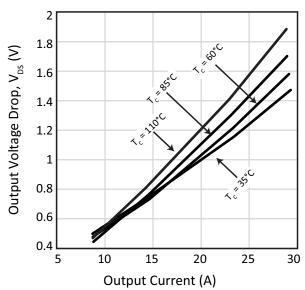

Figure 9: Output Voltage vs. Output Current (Low Side FET)

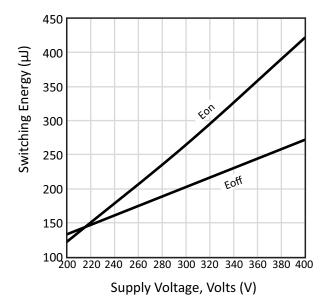

Figure 11: Switching Energy vs. Supply Voltage

Figure 10: Output Voltage Drop vs. Output Current (High Side FET)

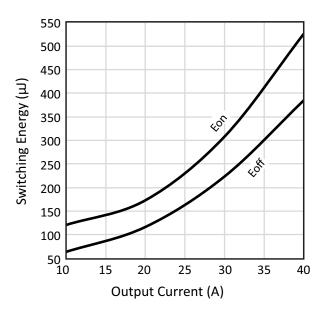

Figure 12: Switching Energy vs. Current

#### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexanalog.com for Apex Microtechnology's complete Application Notes library, Technical Seminar Workbook, and Evaluation Kits.

## **BOOTSTRAP CIRCUIT**

When operating the device with Single Supply Rail, at the high-side supply voltage (V<sub>CC,HS</sub>) can be realized through a bootstrap circuit if operating the device at 100% duty cycle is not required. Figure 13 illustrates the components required for the bootstrap circuit. The high-side supply voltage is connected to the low-side supply voltage through a resistor and a diode that are put in series.

**SA111** +VS 3.3Ω **ENA** ENA OUT  $\mathsf{IN}_{\mathsf{HS}}$ Gate HS  $IN_{IS}$ Driver LS - $V_{CC,LS}$ +18V  $V_{\underline{\mathsf{REG}}}$ 1μF ± **DGND GND**

Figure 13: Bootstrap Circuit for Single Supply Rail Operation

#### POWER SUPPLY FOR DUAL RAIL MODE

In dual rail mode, the low-side gate driver is operating relative to the negative supply rail, which is not ground, but -V<sub>S</sub>. Dual rail mode is typically used when you switch only one side (high side or low side) during each half period of an output sine wave, so a bootstrap circuit for the high-side is also not suitable. Figure 14 shows a simplified power supply for such condition. It is a fly-back converter circuit with two windings on the secondary side of the transformer.

OUT +24V GND OUT VIN LDO UVLO SW IN OUT INTV ADJ GND  $\mathsf{R}_{\mathsf{REF}}$ TC GND

Figure 14: Power Supply for Dual Rail Mode (Simplified)

### INPUT SIGNAL ISOLATION

When using dual rail mode, the input signals (which are referenced to the system ground) need to be level shifted relative to the  $-V_S$  supply. The isoPower devices from Analog Devices are well suited to do that level shifting.

The same circuit also can be used when full isolation of the input signals to the SA111 • SA111A is desired.

$V_{DD1}$  $V_{DD2}$ +5V or +3.3V GND<sub>ISO (23</sub> GND<sub>4</sub> I/O<sub>1A</sub> I/O<sub>2A</sub> uC\_IN<sub>us</sub> 4-CHANNEL iCoupler CORE I/O<sub>1B</sub> I/O<sub>2B</sub>  $uC_IN_{LS}$ I/O<sub>1C</sub> ADuM5410 I/O<sub>2C</sub> ENA uC\_ENA I/O<sub>1D</sub> I/O<sub>2D</sub> V<sub>E2</sub> NIC NIC NIC GND<sub>4</sub> GND<sub>ISO</sub>(1 PDIS V<sub>SEL</sub>  $V_{DDP}$ VISC osc RECT REG GND.

Figure 15: Input Signal Isolation (Example using ADuM5410)

### UNDER-VOLTAGE LOCKOUT FUNCTION

The SA111 • SA111A has a built-in under-voltage lockout function. When the V<sub>CC,HS</sub> or V<sub>CC,LS</sub> drops below approximately 9V, the output pin will be high impedance. When the supply voltages rise above approximately 10V, the output will return back to normal operating mode. In addition, to prevent malfunctions due to noise, a mask time of approximately 2.5µs is set on both high side supply voltages.

#### **BYPASSING**

Adequate bypassing of the power supplies is required for proper operation. Failure to do so can cause erratic and low efficiency operation as well as excessive ringing at the outputs. The  $V_S$  supply should be bypassed with at least a 1µF ceramic capacitor in parallel with another low ESR capacitor of a least 10µF per amp of output current. Capacitor types rated for switching applications are the only types that should be considered. The 1µF ceramic capacitor must be physically connected directly to the +/- $V_S$  and POWER GND pins. Even one inch of lead length will cause excessive ringing at the outputs. This is due to the very fast switching times and the inductance of the lead connection. The bypassing requirements of the  $V_{CC}$  supply are less stringent, but still necessary. A  $0.1\mu F$  to  $0.47\mu F$  ceramic capacitor connected directly to the  $V_{CC,LS}$  and  $V_{CC,HS}$  pins will suffice.

### **POWER SUPPLY PROTECTION**

Unidirectional transient Voltage suppressors are recommended as protection on the supply pins as shown in Figure 3. TVS diodes clamp transients to voltages within the power supply rating and clamp power supply reversals to ground. Whether the TVS diodes are used or not, the system power supply should be evaluated for transient performance including power-on overshoot and power-off polarity reversal as well as line regulation. Conditions which can cause open circuits or polarity reversals on either power supply rail should be avoided or protected against. Unidirectional TVS diodes prevent this, and it is desirable that they be both electrically and physically as close to the amplifier as possible.

#### **OUTPUT PROTECTION**

Two external diodes as shown in Figure 3, are required to protect these amplifiers from flyback (kickback) pulses exceeding the supply voltages of the amplifier when driving inductive loads. For component selection, these external diodes must be very quick, such as ultra fast recovery diodes with no more than 200 nanoseconds of reverse recovery time. The diode will turn on to divert the flyback energy into the supply rails thus protecting the output transistors from destruction due to reverse bias.

A note of caution about the supply. The energy of the flyback pulse must be absorbed by the power supply. As a result, a transient will be superimposed on the supply voltage, the magnitude of the transient being a function of its transient impedance and current sinking capability. If the supply voltage plus transient exceeds the maximum supply rating or if the AC impedance of the supply is unknown, it is best to clamp the output and the supply with a zener diode to absorb the transient.

#### INPUT PROTECTION

It is recommended to connect two Schottky diodes at the ENA,  $IN_{LS}$  pins to provide external protection for the SA111 • SA111A, as shown in Figure 16. A 100pF capacitor (capacitor C) can be connected to ground to provide ESD protection from coaxial cables and other ESD sources. A series resistor (approximately 200 $\Omega$ ) may be added in series with the input pins to limit excessive current going into pins.

**Figure 16: Input Protection**

# **SA111**

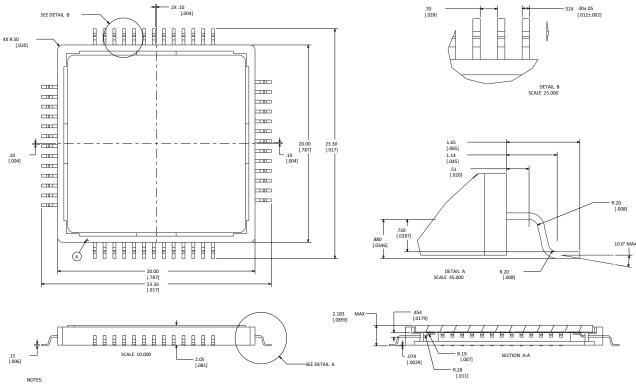

### **PACKAGE AND DEVICE OPTIONS**

| Part Number | Apex Package Style | Description                             | MSL <sup>1</sup> |

|-------------|--------------------|-----------------------------------------|------------------|

| SA111       | PR                 | 52-pin Surface-Mount Package, QFP Style | Level 6          |

| SA111A      | PR                 | 52-pin Surface-Mount Package, QFP Style | Level 6          |

1. The Moisture Sensitivity Level rating according to the JEDEC industry standard classification.

- NOTES:

1. OVERALL THICKNESS NOT TO EXCEED 2.18MM.

2. INTERNAL LEADS RADIUS CAN CHANGE NEED BE.

3. ENTIRE LEAD MAY BE LOWERED IN CONJUNCTION WITH IMS BOARD.

4. PIN ONE NIDICATOR.

#### **NEED TECHNICAL HELP? CONTACT APEX SUPPORT!**

For all Apex Microtechnology product questions and inquiries, call toll free 800-546-2739 in North America. For inquiries via email, please contact apex.support@apexanalog.com. International customers can also request support by contacting their local Apex Microtechnology Sales Representative. To find the one nearest to you, go to www.apexanalog.com

#### IMPORTANT NOTICE

Apex Microtechnology, Inc. has made every effort to insure the accuracy of the content contained in this document. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (expressed or implied). Apex Microtechnology reserves the right to make changes without further notice to any specifications or products mentioned herein to improve reliability. This document is the property of Apex Microtechnology and by furnishing this information, Apex Microtechnology grants no license, expressed or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Apex Microtechnology owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Apex Microtechnology integrated circuits or other products of Apex Microtechnology. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

APEX MICROTECHNOLOGY PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN PRODUCTS USED FOR LIFE SUPPORT, AUTOMOTIVE SAFETY, SECURITY DEVICES, OR OTHER CRITICAL APPLICATIONS. PRODUCTS IN SUCH APPLICATIONS ARE UNDERSTOOD TO BE FULLY AT THE CUSTOMER OR THE CUSTOMER'S RISK.

Apex Microtechnology, Apex and Apex Precision Power are trademarks of Apex Microtechnology, Inc. All other corporate names noted herein may be trademarks of their respective holders.